- 您现在的位置:买卖IC网 > Sheet目录2000 > IDT82V3202NLG (IDT, Integrated Device Technology Inc)IC PLL WAN EBU SGL 68-VFQFPN

IDT82V3202

EBU WAN PLL

Electrical Specifications

107

September 11, 2009

8.7

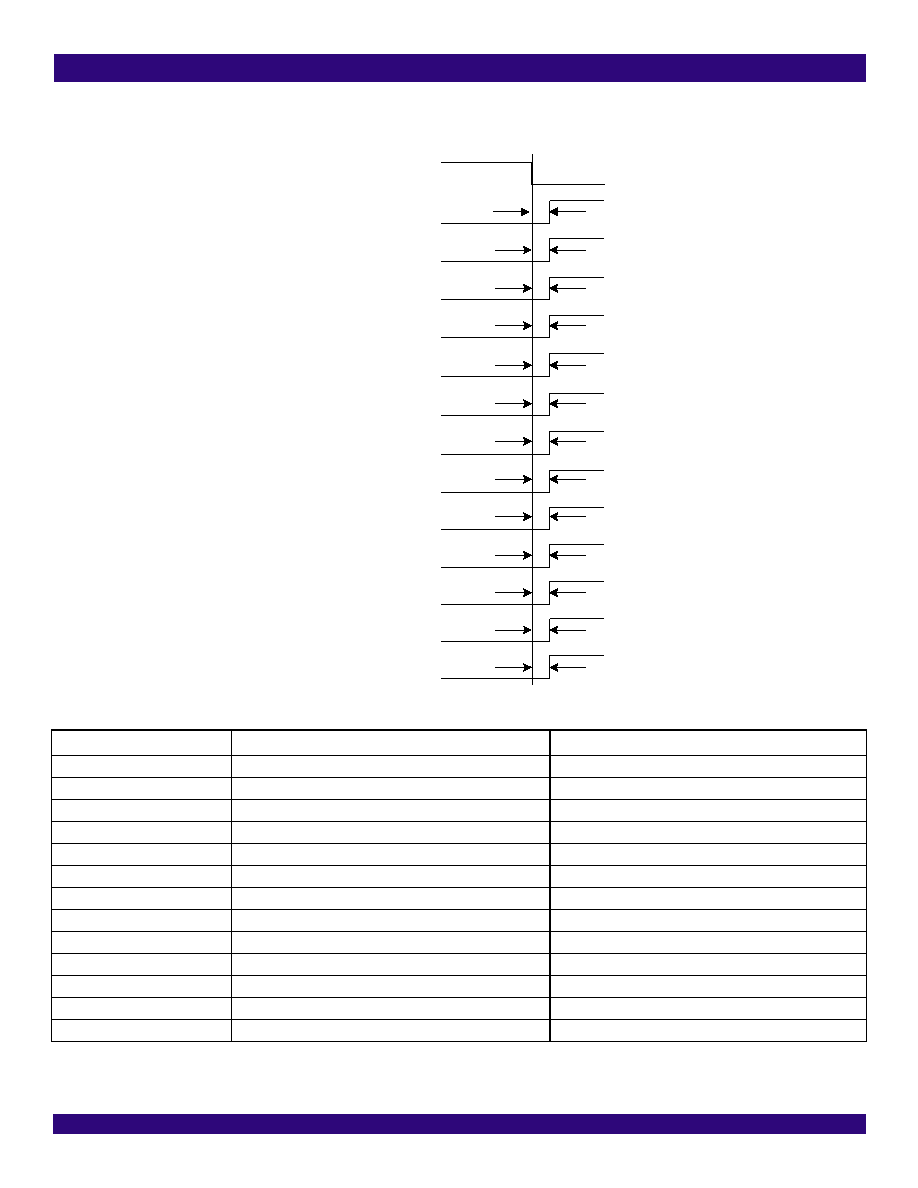

OUTPUT CLOCK TIMING

Table 50: Output Clock Timing

Symbol

Typical Delay (ns)

Peak to Peak Delay Variation (ns)

t1

02

t2

02

t3

02

t4

02

t5

02

t6

02

t7

02

t8

02

t9

02

t10

02

t11

01.5

t12

0

1.5 (not recommended to use)

t13

0

1.5 (not recommended to use)

N X T1 (1.544 MHz)

t

1

N X E1 (2.048 MHz)

E3 (34.368 MHz)

6.48 MHz

19.44 MHz

25.92 MHz

38.88 MHz

51.84 MHz

77.76 MHz

155.52 MHz

311.04 MHz

622.08 MHz

FRSYNC_8K

T3 (44.736 MHz)

t

2

t

3

t

4

t

5

t

6

t

7

t

8

t

9

t

10

t

11

t

12

t

13

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

IDT82V3255TFG

IC PLL WAN SMC STRATUM 3 64-TQFP

IDT82V3280APFG

IC PLL WAN SE STRATUM 2 100TQFP

IDT82V3285AEQG

IC PLL WAN SE STRATUM 100TQFP

IDT82V3285EQG

IC PLL WAN SE STRATUM 100TQFP

IDT82V3288BCG

IC PLL WAN 3E STRATUM 2 208CABGA

IDT82V3355EDG

IC PLL WAN SYNC ETHERNET 64TQFP

IDT82V3358EDG

IC PLL WAN SYNC ETHERNET 64TQFP

IDTCSPT857DNLG8

IC PLL CLK DVR SDRAM 40-VFQFPN

相关代理商/技术参数

IDT82V3202NLG8

功能描述:IC PLL WAN EBU SGL 68-VFQFPN RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT

IDT82V3202NLGBLANK

制造商:IDT 制造商全称:Integrated Device Technology 功能描述:EBU WAN PLL

IDT82V3255

制造商:IDT 制造商全称:Integrated Device Technology 功能描述:WAN PLL

IDT82V3255_08

制造商:IDT 制造商全称:Integrated Device Technology 功能描述:WAN PLL

IDT82V3255DK

制造商:IDT 制造商全称:Integrated Device Technology 功能描述:WAN PLL

IDT82V3255DKG

功能描述:IC PLL WAN SMC STRATUM 3 64-TQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT

IDT82V3255DKG8

功能描述:IC PLL WAN SMC STRATUM 3 64-TQFP RoHS:是 类别:集成电路 (IC) >> 时钟/计时 - 专用 系列:- 标准包装:1,500 系列:- 类型:时钟缓冲器/驱动器 PLL:是 主要目的:- 输入:- 输出:- 电路数:- 比率 - 输入:输出:- 差分 - 输入:输出:- 频率 - 最大:- 电源电压:3.3V 工作温度:0°C ~ 70°C 安装类型:表面贴装 封装/外壳:28-SSOP(0.209",5.30mm 宽) 供应商设备封装:28-SSOP 包装:带卷 (TR) 其它名称:93786AFT

IDT82V3255EDGBLANK

制造商:IDT 制造商全称:Integrated Device Technology 功能描述:WAN PLL